# MIPS64<sup>TM</sup> 5K<sup>TM</sup> Processor Core Family Software User's Manual

Document Number: MD00012 Revision 02.08 May 28, 2002

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 1999-2002 MIPS Technologies Inc. All right reserved.

Copyright © 1999-2002 MIPS Technologies, Inc. All rights reserved.

Unpublished rights reserved under the Copyright Laws of the United States of America.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying, or use of this information (in whole or in part) which is not expressly permitted in writing by MIPS Technologies or a contractually-authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

MIPS Technologies or any contractually-authorized third party reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error of omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Any license under patent rights or any other intellectual property rights owned by MIPS Technologies or third parties shall be conveyed by MIPS Technologies or any contractually-authorized third party in a separate license agreement between the parties.

The information contained in this document shall not be exported or transferred for the purpose of reexporting in violation of any U.S. or non-U.S. regulation, treaty, Executive Order, law, statute, amendment or supplement thereto.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or any contractually-authorized third party.

MIPS®, R3000®, R4000®, R5000® and R10000® are among the registered trademarks of MIPS Technologies, Inc. in the United States and certain other countries, and MIPS16<sup>TM</sup>, MIPS16e<sup>TM</sup>,MIPS32<sup>TM</sup>, MIPS64<sup>TM</sup>, MIPS-3D<sup>TM</sup>, MIPS-based<sup>TM</sup>, MIPS II<sup>TM</sup>, MIPS III<sup>TM</sup>, MIPS III<sup>TM</sup>, MIPS IV<sup>TM</sup>, MIPS V<sup>TM</sup>, MDMX<sup>TM</sup>, SmartMIPS<sup>TM</sup>, 4K<sup>TM</sup>, 4Kc<sup>TM</sup>, 4Km<sup>TM</sup>, 4Kp<sup>TM</sup>, 4KEc<sup>TM</sup>, 4KEm<sup>TM</sup>, 4KEp<sup>TM</sup>, 4KSc<sup>TM</sup>, 5K<sup>TM</sup>, 5Kc<sup>TM</sup>, 5Kc<sup>TM</sup>, 5Kf<sup>TM</sup>, 20Kc<sup>TM</sup>, R20K<sup>TM</sup>, R4300<sup>TM</sup>, ATLAS<sup>TM</sup>, CoreLV<sup>TM</sup>, EC<sup>TM</sup>, JALGO<sup>TM</sup>, MALTA<sup>TM</sup>, MGB<sup>TM</sup>, SEAD-2<sup>TM</sup>, SOC-it<sup>TM</sup> and YAMON<sup>TM</sup> are among the trademarks of MIPS Technologies, Inc.

All other trademarks referred to herein are the property of their respective owners.

# Table of Contents

| Chapter 1 Introduction                                                        | 1  |

|-------------------------------------------------------------------------------|----|

| 1.1 Overview                                                                  | 1  |

| 1.2 Features                                                                  | 2  |

| 1.3 Core Block Diagram                                                        | 4  |

| 1.3.1 Execution Unit                                                          | 4  |

| 1.3.2 Floating Point Unit (FPU) / Coprocessor 1 (5Kf core only)               | 5  |

| 1.3.3 Multiply/Divide Unit (MDU)                                              | 5  |

| 1.3.4 System Control Coprocessor (CP0)                                        | 6  |

| 1.3.5 Memory Management Unit (MMU)                                            | 6  |

| 1.3.6 Cache Controllers & Bus Interface                                       |    |

| 1.3.7 Power Management                                                        | 6  |

| 1.3.8 Instruction and Data Caches                                             | 6  |

| 1.3.9 EJTAG Debug Support                                                     | 7  |

| Chapter 2 Pipeline                                                            | 9  |

| 2.1 Pipeline Stages                                                           | 9  |

| 2.1.1 I Stage: Instruction Fetch                                              | 10 |

| 2.1.2 D Stage: Instruction Dispatch                                           | 10 |

| 2.1.3 R Stage: Register File Read                                             | 10 |

| 2.1.4 E Stage: Execution                                                      | 10 |

| 2.1.5 M Stage: Memory Access                                                  | 11 |

| 2.1.6 W Stage: Writeback                                                      | 11 |

| 2.2 Instruction Fetch                                                         | 11 |

| 2.3 Branch Delay                                                              | 12 |

| 2.4 Limited Dual Issue                                                        | 13 |

| 2.5 Instruction Fetching from Uncached Memory Space                           | 15 |

| 2.6 Data Access                                                               | 16 |

| 2.7 Instruction Scheduling                                                    | 16 |

| 2.8 MDU Pipeline                                                              | 16 |

| 2.8.1 Multiply/MAC Operations                                                 | 16 |

| 2.8.2 Divide Operations                                                       | 18 |

| 2.8.3 Latencies and Repeat Rates                                              | 19 |

| 2.8.4 MDU Interaction with Integer Unit Pipeline                              | 20 |

| 2.9 Slip Conditions and Interlock Handling                                    | 21 |

| Chapter 3 Floating-Point Unit                                                 |    |

| 3.1 Features Overview                                                         |    |

| 3.1.1 IEEE Standard 754                                                       | 28 |

| 3.2 Enabling the Floating-Point Coprocessor                                   | 28 |

| 3.3 Data Formats                                                              | 28 |

| 3.3.1 Floating-Point Formats                                                  | 29 |

| 3.3.2 Fixed-Point Formats                                                     | 32 |

| 3.4 Floating-Point General Registers                                          | 32 |

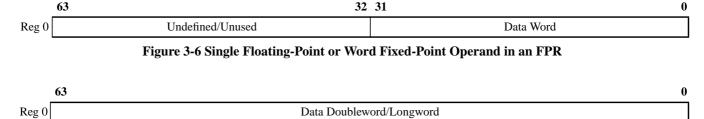

| 3.4.1 FPRs and Formatted Operand Layout                                       | 33 |

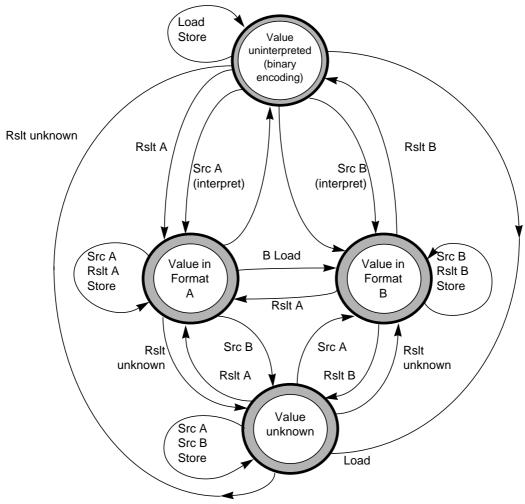

| 3.4.2 Formats of Values Used in FP Registers                                  | 33 |

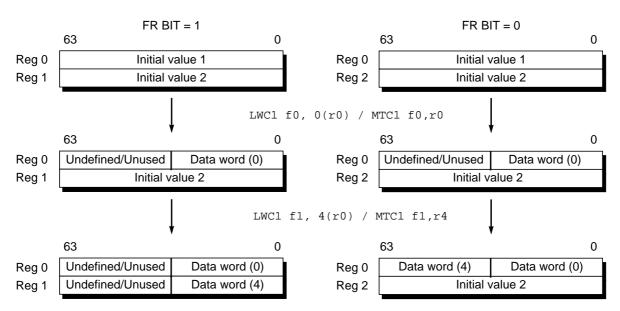

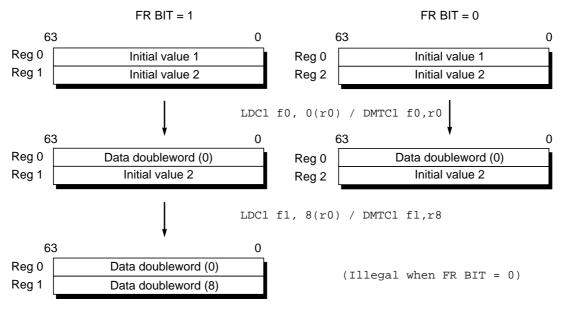

| 3.4.3 Binary Data Transfers (32-Bit and 64-Bit)                               | 34 |

| 3.5 Floating-Point Control Registers                                          | 35 |

| 3.5.1 Floating-Point Implementation Register (FIR, CP1 Control Register 0)    | 37 |

| 3.5.2 Floating-Point Condition Codes Register (FCCR, CP1 Control Register 25) | 38 |

| 3.5.3 Floating-Point Exceptions Register (FEXR, CP1 Control Register 26)      |    |

| 3.5.4 Floating-Point Enables Register (FENR, CP1 Control Register 28)         | 39 |

| 3.5.5 Floating-Point Control and Status Register (FCSR, CP1 Control Register 31) |    |

|----------------------------------------------------------------------------------|----|

| 3.5.7 FCSR Cause Bit Update Flow                                                 |    |

| 3.5.7 FCSR Cause Bit Opuate Flow  3.6 Instruction Overview                       |    |

| 3.6.1 Data Transfer Instructions                                                 |    |

| 3.6.2 Arithmetic Instructions                                                    |    |

| 3.6.3 Conversion Instructions                                                    |    |

| 3.6.4 Formatted Operand-Value Move Instructions                                  |    |

| 3.6.5 Conditional Branch Instructions                                            |    |

| 3.6.6 Miscellaneous Instructions                                                 |    |

| 3.7 Exceptions                                                                   |    |

| 3.7.1 Precise Exception Mode                                                     |    |

| 3.7.2 Exception Conditions                                                       |    |

| 3.8 Pipeline and Performance                                                     |    |

| 3.8.1 Pipeline Overview                                                          |    |

| 3.8.2 Bypassing                                                                  |    |

| 3.8.3 Repeat Rate and Latency                                                    |    |

| 3.6.3 Repeat Rate and Latency                                                    |    |

| Chapter 4 Memory Management                                                      | 59 |

| 4.1 Introduction                                                                 | 59 |

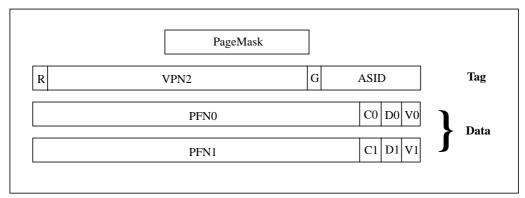

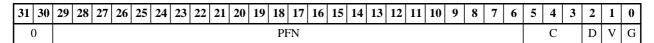

| 4.2 TLB Organization                                                             | 59 |

| 4.2.1 PageMask Field                                                             | 60 |

| 4.2.2 ASID, GLOBAL, and R Bits                                                   | 60 |

| 4.2.3 Dirty Bit                                                                  | 61 |

| 4.2.4 Cache/Coherency Attributes                                                 |    |

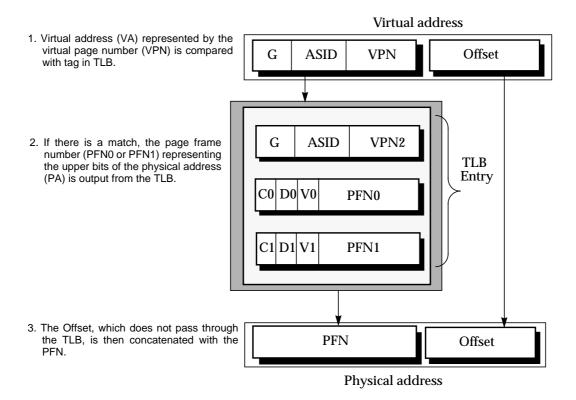

| 4.3 Address Translation                                                          | 61 |

| 4.4 TLB Implementation Details                                                   | 63 |

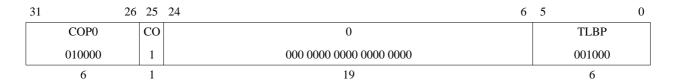

| 4.5 TLB Management Instructions                                                  | 64 |

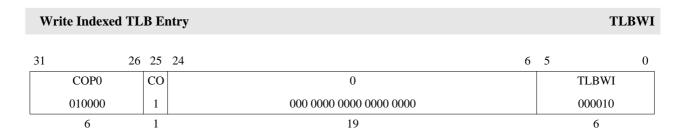

| 4.5.1 TLBWI - TLB Write Indexed                                                  | 64 |

| 4.5.2 TLBWR - TLB Write Random                                                   |    |

| 4.5.3 TLBP - TLB Probe                                                           | 65 |

| 4.5.4 TLBR - TLB Read Indexed                                                    | 65 |

| 4.6 TLB Exceptions                                                               | 65 |

| 4.6.1 TLB Refill Exception                                                       | 66 |

| 4.6.2 TLB Invalid Exception                                                      |    |

| 4.6.3 TLB Modified Exception                                                     | 66 |

| 4.6.4 Machine Check (TLB Shutdown)                                               | 66 |

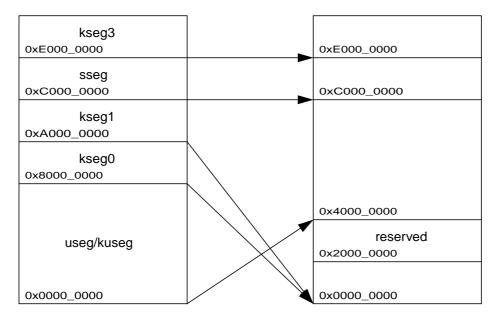

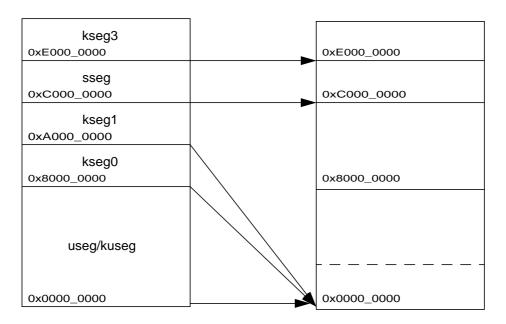

| 4.7 TLB Memory Maps                                                              |    |

| 4.7.1 Access Control as a Function of Address and Operating Mode                 |    |

| 4.7.2 Address Translation and Cache Coherency Attributes for kseg0 and kseg1     | 72 |

| 4.7.3 Address Translation and Cache Coherency Attributes for xkphys              |    |

| 4.7.4 Address Translation for kuseg when StatusERL = 1                           |    |

| 4.7.5 Address Translation in Debug Mode                                          |    |

| 4.8 FMT Memory Maps                                                              |    |

| 4.8.1 User Mode (useg/suseg/kuseg)                                               | 75 |

| 4.8.2 Supervisor Mode (sseg)                                                     |    |

| 4.8.3 Kernel Mode (kseg0, kseg1 and kseg3)                                       |    |

| 4.8.4 Debug Mode                                                                 | 77 |

| Chapter 5 Exception Processing                                                   | 70 |

| 5.1 Overview                                                                     |    |

|                                                                                  |    |

| 5.1.1 Interrupt and NMI Latency                                                  |    |

| 5.1.2 Exception Vector Locations                                                 |    |

| 5.1.4 General Exception Processing                                               |    |

| 5.1.4 General Exception Flocessing  5.2 Reset Exception                          |    |

| 5.2 Reset Exception                                                              | 03 |

| 5.3 Soft Reset Exception                                                  | 84  |

|---------------------------------------------------------------------------|-----|

| 5.4 Non-maskable Interrupt (NMI) Exception                                | 85  |

| 5.5 Machine Check Exception                                               | 86  |

| 5.6 Address Error Exception                                               | 86  |

| 5.7 TLB and XTLB Refill Exceptions                                        | 87  |

| 5.8 TLB Invalid Exception                                                 | 88  |

| 5.9 TLB Modified Exception                                                | 89  |

| 5.10 Cache Error Exception                                                | 89  |

| 5.11 Bus Error Exception                                                  | 90  |

| 5.12 Integer Overflow Exception                                           | 91  |

| 5.13 Trap Exception                                                       | 91  |

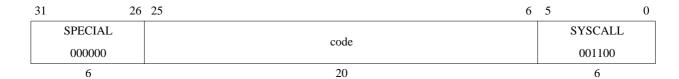

| 5.14 System Call Exception                                                | 91  |

| 5.15 Breakpoint Exception                                                 | 92  |

| 5.16 Reserved Instruction Exception                                       |     |

| 5.17 Coprocessor Unusable Exception                                       | 92  |

| 5.18 MDMX Coprocessor Unusable Exception                                  |     |

| 5.19 Floating-Point Exception                                             |     |

| 5.20 Coprocessor 2 Exception                                              |     |

| 5.21 Watch Exception                                                      |     |

| 5.22 Interrupt Exception                                                  |     |

| 5.23 Debug Exceptions                                                     |     |

| 5.23.1 Exception Handling of Debug Exceptions                             |     |

| 5.23.2 Debug Breakpoint Exception                                         |     |

| 5.23.3 Debug Instruction Break Exception                                  |     |

| 5.23.4 Debug Data Break Load/Store Exception                              |     |

| 5.23.5 Debug Data Break Load Imprecise Exception                          |     |

| 5.23.6 Debug Single Step Exception                                        |     |

| 5.23.7 Debug Interrupt Exception                                          |     |

| 5.23.8 Handling of Exceptions in Debug Mode                               |     |

| 5.23.9 EJTAG Boot                                                         |     |

| Chapter 6 Coprocessor 0 Registers                                         | 103 |

| 6.1 Index Register (CP0 Register 0, Select 0)                             |     |

| 6.2 Random Register (CP0 Register 1, Select 0)                            |     |

| 6.3 EntryLo0, EntryLo1 (CP0 Registers 2 and 3, Select 0)                  |     |

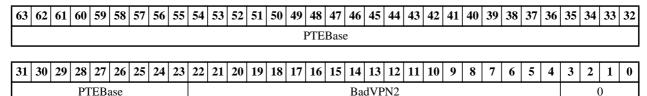

| 6.4 Context Register (CP0 Register 4, Select 0)                           |     |

| 6.5 PageMask Register (CP0 Register 5, Select 0)                          |     |

| 6.6 Wired Register (CPO Register 6, Select 0)                             | 108 |

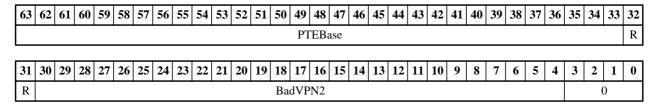

| 6.7 BadVAddr Register (CP0 Register 8, Select 0)                          |     |

| 6.8 Count Register (CP0 Register 9, Select 0)                             |     |

| 6.9 EntryHi Register (CP0 Register 10, Select 0)                          |     |

| 6.10 Compare Register (CP0 Register 11, Select 0)                         |     |

| 6.11 Status Register (CP Register 12, Select 0)                           |     |

|                                                                           |     |

| 6.12 Cause Register (CP0 Register 13, Select 0)                           |     |

| 6.13 Exception Program Counter (CP0 Register 14, Select 0)                |     |

| 6.14 Processor Identification (CPO Register 15, Select 0)                 |     |

| 6.15 Configuration Register (CP0 Register 16, Select 0)                   |     |

| 6.16 Configuration Register 1 (CP0 Register 16, Select 1)                 |     |

| 6.17 WatchLo Register (CP0 Register 18)                                   |     |

| 6.18 WatchHi Register (CP0 Register 19)                                   |     |

| 6.19 XContext Register (CP0 Register 20, Select 0)                        |     |

| 6.20 Debug Register (CP0 Register 23, Select 0)                           |     |

| 6.21 Debug Exception Program Counter Register (CP0 Register 24, Select 0) |     |

| 6.22 Performance Counter Register (CP0 Register 25, select 0-3)           |     |

| 6.23 ErrCtl Register (CP0 Register 26, Select 0)                          |     |

| 6.24 CacheErr Register (CP0 Register 27, Select 0)                        | 135 |

| 6.25 TagLo Register (CP0 Register 28, Select 0)      |     |

|------------------------------------------------------|-----|

| 6.26 DataLo Register (CP0 Register 28, Select 1)     |     |

| 6.27 TagHi Register (CP0 Register 29, Select 0)      |     |

| 6.28 DataHi Register (CP0 Register 29, Select 1)     |     |

| 6.29 ErrorEPC (CP0 Register 30, Select 0)            |     |

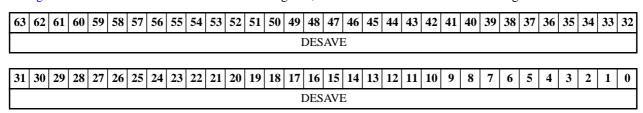

| 6.30 Debug Exception SAVE (DESAVE) (CP0 register 31) | 140 |

| Chapter 7 Hardware and Software Initialization       | 141 |

| 7.1 Hardware-Initialized Processor State             |     |

| 7.1.1 Coprocessor 0 State                            |     |

| 7.1.2 TLB Initialization                             |     |

| 7.1.3 Bus State Machines                             |     |

| 7.1.4 Static Configuration Inputs                    |     |

| 7.1.5 Fetch Address                                  |     |

| 7.2 Software-Initialized Processor State             |     |

| 7.2.1 Coprocessor 0 Registers                        |     |

| 7.2.2 Register File                                  |     |

| 7.2.3 TLB                                            |     |

| 7.2.4 Caches                                         |     |

|                                                      |     |

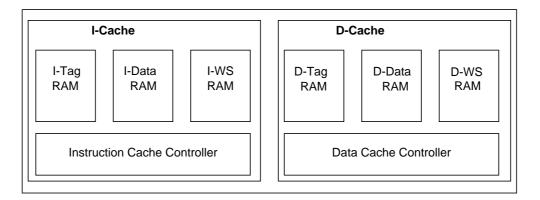

| Chapter 8 Cache Organization and Operation           |     |

| 8.1 Introduction                                     |     |

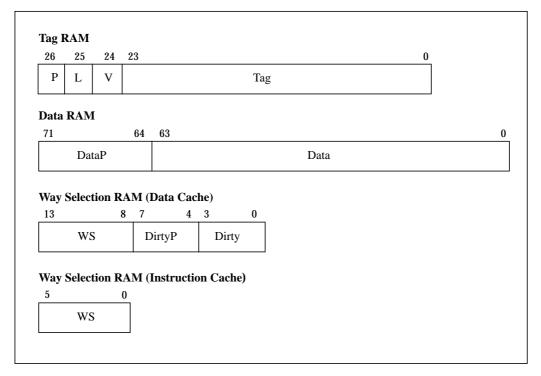

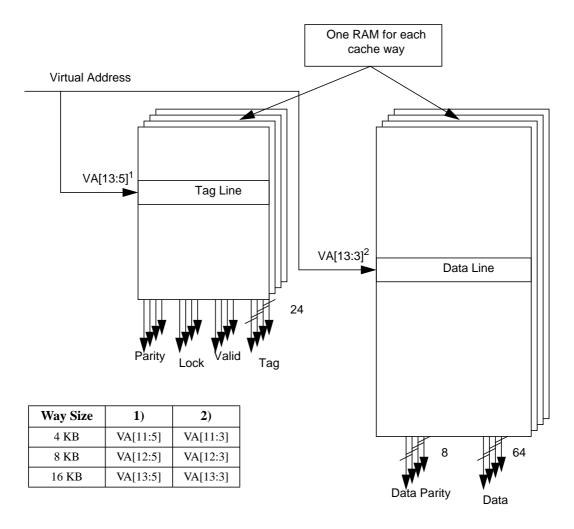

| 8.2 Cache Organization                               |     |

| 8.2.1 Instruction Cache Access                       |     |

| 8.2.2 Data Cache Access                              |     |

| 8.3 Cache Write Policies                             |     |

| 8.3.1 Write Through, No Write Allocate               |     |

| 8.3.2 Write Through, Write Allocate                  |     |

| 8.3.3 Write Back, Write Allocate                     |     |

| 8.3.4 Uncached                                       |     |

| 8.4 Cached Loads and Fetches                         |     |

| 8.5 Uncached Loads and Fetches                       |     |

| 8.6 Way Selection Algorithm                          |     |

| 8.7 Write Buffer                                     |     |

| 8.8 Read Buffer                                      |     |

| 8.9 Transaction Priority                             |     |

| 8.10 CACHE Instruction                               |     |

| 8.11 PREF and PREFX Instructions                     |     |

| 8.12 Error Handling                                  |     |

| 8.12.1 Parity                                        |     |

| 8.12.2 WS Field Error                                |     |

| 8.12.3 Bus Errors                                    | 155 |

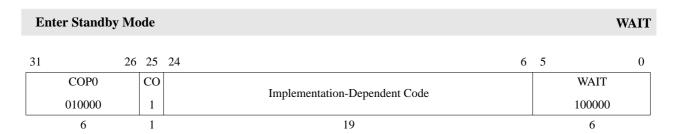

| Chapter 9 Power Management                           | 157 |

| 9.1 Register-Controlled Power Management             |     |

| 9.2 Instruction-Controlled Power Management          |     |

|                                                      |     |

| Chapter 10 EJTAG Debug Features                      |     |

| 10.1 Introduction                                    |     |

| 10.1.1 EJTAG Components and Options                  |     |

| 10.1.2 Register and Memory Map Overview              |     |

| 10.1.3 Register Field Notations                      |     |

| 10.2 EJTAG Processor Extensions                      |     |

| 10.2.1 Debug Exceptions                              |     |

| 10.2.2 Debug Mode Execution                          | 163 |

| 10.2.3 Debug Mode Handling of Processor Resources    |     |

| 10.2.4 EJTAG Coprocessor 0 Registers                 | 165 |

| 10.2.5 Debug Mode Address Space                                           | 166 |

|---------------------------------------------------------------------------|-----|

| 10.2.6 Interrupts and NMIs                                                | 168 |

| 10.2.7 Reset and Soft Reset of Processor                                  | 168 |

| 10.3 Debug Control Register                                               | 169 |

| 10.4 Hardware Breakpoints                                                 |     |

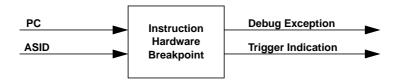

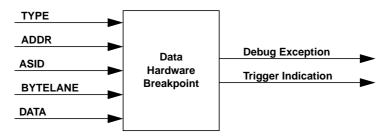

| 10.4.1 Introduction                                                       |     |

| 10.4.2 Overview of Instruction and Data Breakpoint Registers              | 172 |

| 10.4.3 Conditions for Matching Breakpoints                                |     |

| 10.4.4 Debug Exceptions from Breakpoints                                  |     |

| 10.4.5 Breakpoints Used as Triggerpoints                                  |     |

| 10.4.6 Instruction Breakpoint Registers                                   |     |

| 10.4.7 Data Breakpoint Registers                                          |     |

| 10.5 EJTAG Test Access Port                                               |     |

| 10.5.1 Instruction Register and Special Instructions                      |     |

| 10.5.2 TAP Data Registers                                                 |     |

| 10.5.3 Example of EJTAG Memory Access through Processor Access            |     |

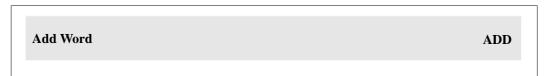

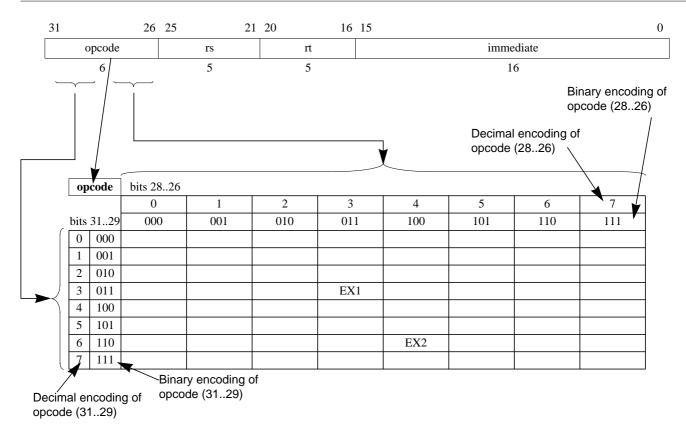

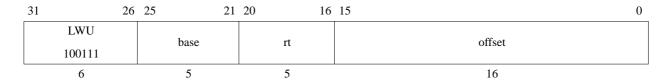

| Chapter 11 Instruction Set Overview                                       | 205 |

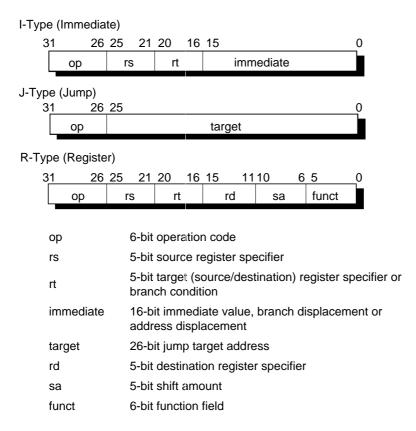

| 11.1 CPU Instruction Formats                                              | 205 |

| 11.2 Load and Store Instructions                                          | 206 |

| 11.2.1 Scheduling a Load Delay Slot                                       | 206 |

| 11.2.2 Access Types                                                       |     |

| 11.3 Computational Instructions                                           | 208 |

| 11.3.1 Cycle Timing for Multiply and Divide Instructions                  | 209 |

| 11.4 Jump and Branch Instructions                                         | 209 |

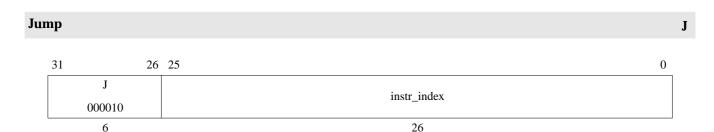

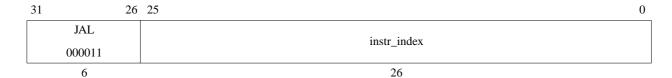

| 11.4.1 Jump Instructions                                                  | 209 |

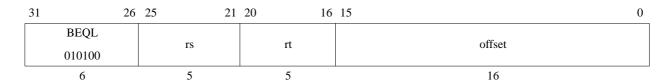

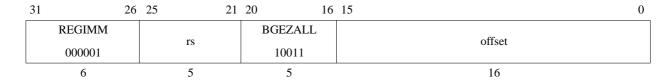

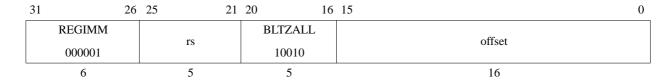

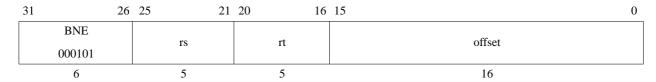

| 11.4.2 Branch Instructions                                                | 209 |

| 11.5 Control Instructions                                                 | 210 |

| 11.6 Coprocessor Instructions                                             | 210 |

| 11.7 Enhancements to the MIPS Architecture                                |     |

| 11.7.1 CLO - Count Leading Ones                                           | 210 |

| 11.7.2 DCLO - Double Count Leading Ones                                   | 210 |

| 11.7.3 CLZ - Count Leading Zeros                                          | 210 |

| 11.7.4 DCLZ - Double Count Leading Zeros                                  | 211 |

| 11.7.5 MADD - Multiply and Add Word                                       | 211 |

| 11.7.6 MADDU - Multiply and Add Unsigned Word                             | 211 |

| 11.7.7 MSUB - Multiply and Subtract Word                                  | 211 |

| 11.7.8 MSUBU - Multiply and Subtract Unsigned Word                        | 211 |

| 11.7.9 MUL - Multiply Word                                                |     |

| Chapter 12 Instructions                                                   | 213 |

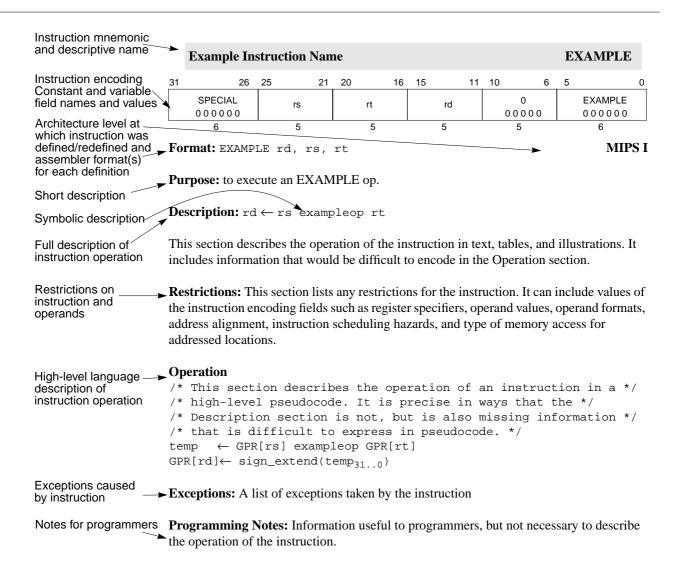

| 12.1 Example Instruction Page                                             | 213 |

| 12.1.1 Instruction Descriptive Name and Mnemonic                          | 214 |

| 12.1.2 Instruction Fields                                                 | 214 |

| 12.1.3 Format Field                                                       | 215 |

| 12.1.4 Purpose Field                                                      | 215 |

| 12.1.5 Description Field                                                  | 215 |

| 12.1.6 Restrictions Field                                                 | 216 |

| 12.1.7 Operation Field                                                    | 216 |

| 12.1.8 Exceptions Field                                                   | 216 |

| 12.2 Coprocessor 0 (CP0) Hazards                                          | 216 |

| 12.2.1 Hazards on CACHE Instructions Modifying Instruction Cache Contents | 220 |

| 12.3 Instruction Summary                                                  | 220 |

| 12.3.1 Basic Instructions                                                 | 220 |

| 12.3.2 FPU Instructions                                                   |     |

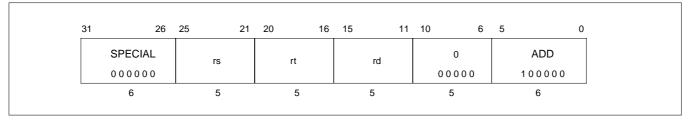

| 12.4 Instruction Bit Encodings                                            | 228 |

| 12.5 Instruction Set        | 233 |

|-----------------------------|-----|

| Annendix A Revision History | 511 |

# List of Figures

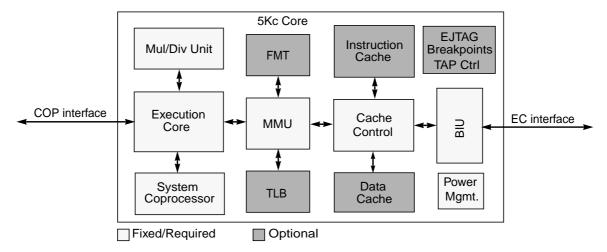

| Figure 1-1: 5Kc Core Block Diagram                                                | 4  |

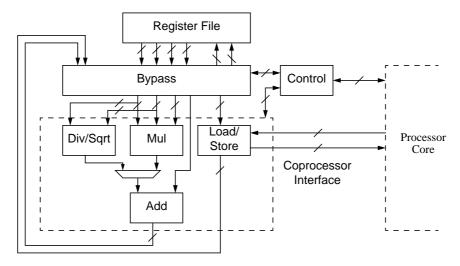

|-----------------------------------------------------------------------------------|----|

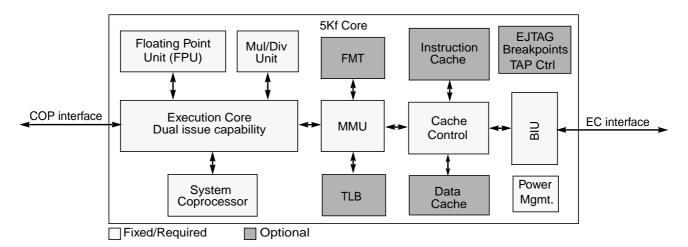

| Figure 1-2: 5Kf Core Block Diagram                                                |    |

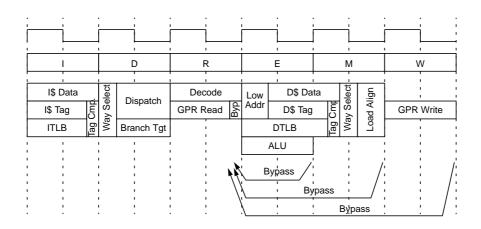

| Figure 2-1: Pipeline Stages                                                       | 10 |

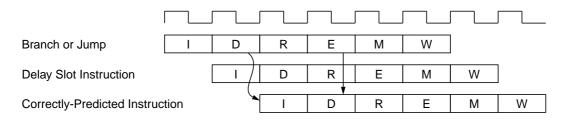

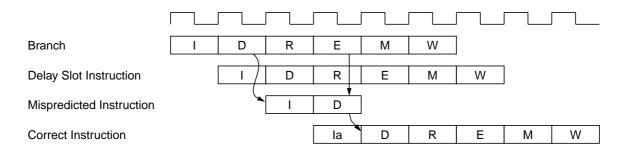

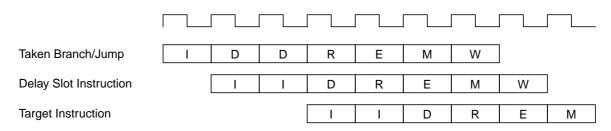

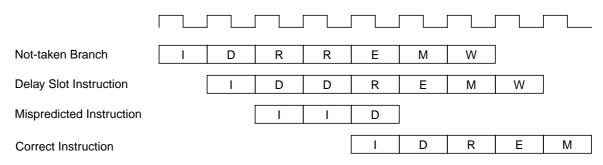

| Figure 2-2: Correctly-predicted Branch                                            |    |

| Figure 2-3: Mispredicted Branch                                                   |    |

| Figure 2-4: Taken Branch/Jump at Even Address Jumps to Instruction at Odd Address |    |

| Figure 2-5: Not-taken Branch At Even Address                                      |    |

| Figure 2-6: Instruction Fetching from Uncached Memory Space                       |    |

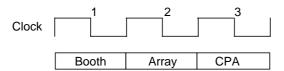

| Figure 2-7: MDU Pipeline Flow During a 32x16 Multiply Operation                   |    |

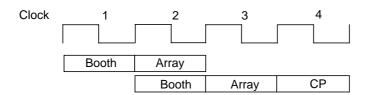

| Figure 2-8: MDU Pipeline Flow During a 32x32 Multiply Operation                   |    |

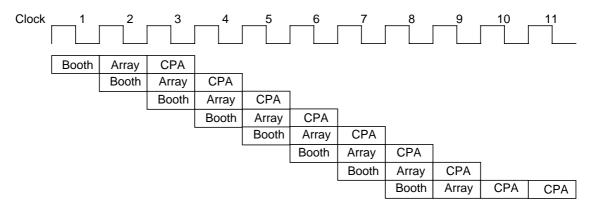

| Figure 2-9: MDU Pipeline Flow During a 64x64 Multiply Operation                   |    |

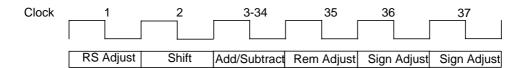

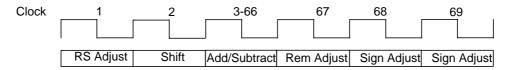

| Figure 2-10: MDU Pipeline Flow During a 32-bit Divide Operation                   |    |

| Figure 2-11: MDU Pipeline Flow During a 64-bit Divide Operation                   |    |

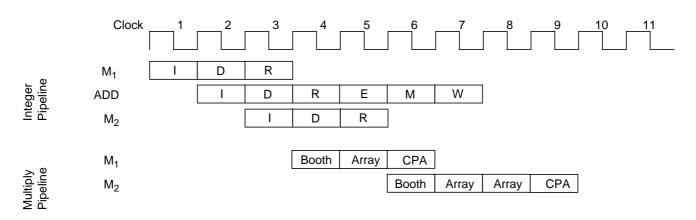

| Figure 2-12: Integer Pipeline and MDU Pipeline Interaction                        |    |

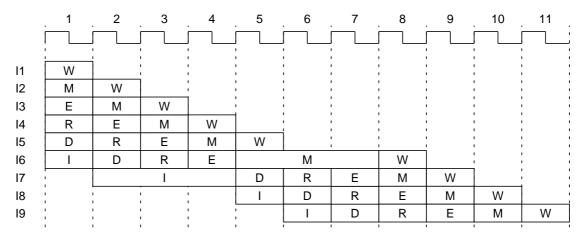

| Figure 2-13: Pipeline Slip                                                        |    |

| Figure 3-1: FPU Block Diagram                                                     |    |

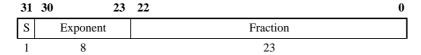

| Figure 3-2: Single-Precision Floating-Point Format (S)                            |    |

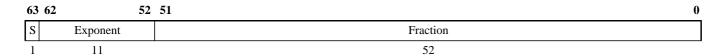

| Figure 3-3: Double-Precision Floating-Point Format (D)                            |    |

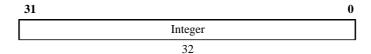

| Figure 3-4: Word Fixed-Point Format (W)                                           |    |

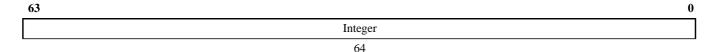

| Figure 3-5: Longword Fixed-Point Format (L)                                       |    |

| Figure 3-6: Single Floating-Point or Word Fixed-Point Operand in an FPR           |    |

| Figure 3-7: Double Floating-Point or Longword Fixed-Point Operand in an FPR       |    |

| Figure 3-8: Effect of FPU Operations on the Format of Values Held in FPRs         |    |

| Figure 3-9: FPU Word Load and Move-to Operations                                  |    |

| Figure 3-10: FPU Doubleword Load and Move-to Operations.                          |    |

| Figure 3-11: FIR Format                                                           |    |

| Figure 3-12: FCCR Format                                                          |    |

| Figure 3-13: FEXR Format                                                          |    |

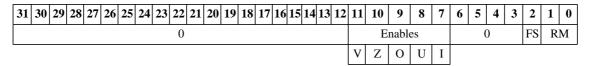

| Figure 3-14: FENR Format                                                          |    |

| Figure 3-15: FCSR Format                                                          |    |

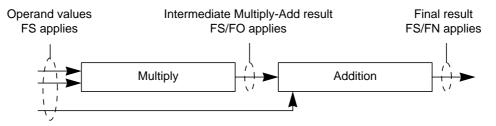

| Figure 3-16: FS/FO/FN Bits Influence on Multiply and Addition Results             |    |

| Figure 3-17: Flushing to Nearest when Rounding Mode is Round to Nearest           |    |

| Figure 3-18: FPU Pipeline                                                         | 55 |

| Figure 3-19: Arithmetic Pipeline Bypass Paths                                     |    |

| Figure 4-1: TLB Entry Format                                                      | 60 |

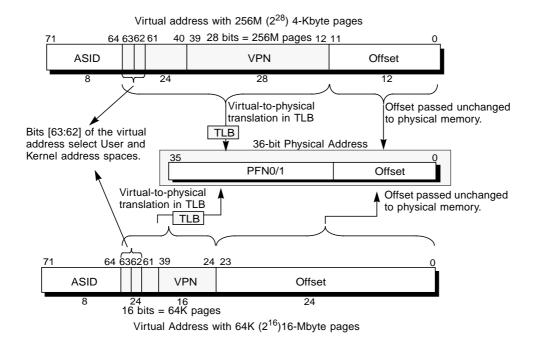

| Figure 4-2: Overview of Virtual-to-Physical Address Translation                   |    |

| Figure 4-3: 64-bit Virtual Address Translation                                    |    |

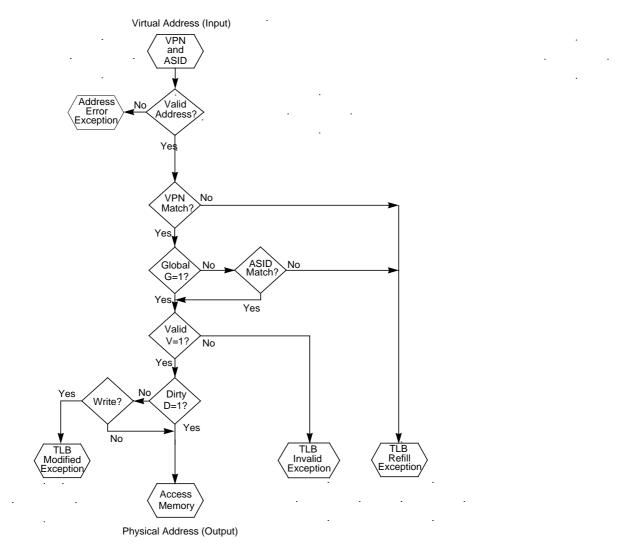

| Figure 4-4: TLB Address Translation and Exception Conditions                      |    |

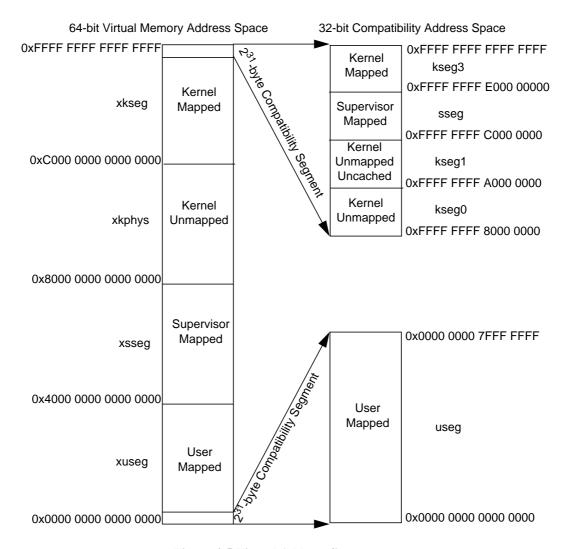

| Figure 4-5: Virtual Address Spaces.                                               |    |

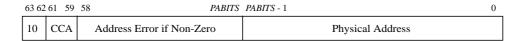

| Figure 4-6: Address Interpretation for xkphys Segment                             |    |

| Figure 4-7: FMT Memory Map (ERL=0)                                                |    |

| Figure 4-8: FMT Memory Map (ERL=1)                                                |    |

| Figure 6-1: Index Register                                                        |    |

| Figure 6-2: Random Register                                                       |    |

| Figure 6-3: EntryLo0, EntryLo1 Register                                           |    |

| Figure 6-4: Context Register                                                      |    |

| Figure 6-5: PageMask Register                                                     |    |

| Figure 6-6: Wired and Random TLB Entries                                          |    |

| Figure 6-7: Wired Register                                                        |    |

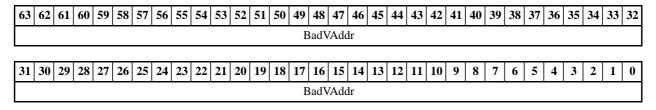

| Figure 6-8: BadVAddr Register                                                     |    |

|                                                                                   |    |

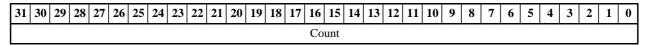

| Figure 6-9: Count Register                                             | 111 |

|------------------------------------------------------------------------|-----|

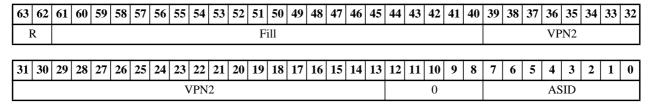

| Figure 6-10: EntryHi Register                                          |     |

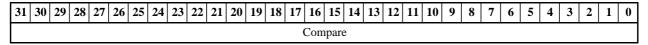

| Figure 6-11: Compare Register                                          |     |

| Figure 6-12: Status Register                                           |     |

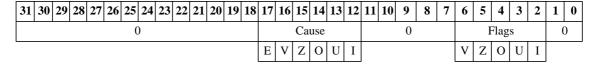

| Figure 6-13: Cause Register                                            |     |

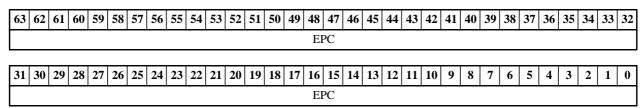

| Figure 6-14: EPC Register                                              |     |

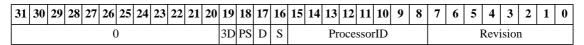

| Figure 6-15: PRId Register                                             |     |

| Figure 6-16: Config Register                                           |     |

| Figure 6-17: Config1 Register                                          |     |

| Figure 6-18: WatchLo Register                                          |     |

| Figure 6-19: WatchHi Register                                          |     |

| Figure 6-20: XContext Register Format.                                 |     |

| Figure 6-21: Debug Register                                            |     |

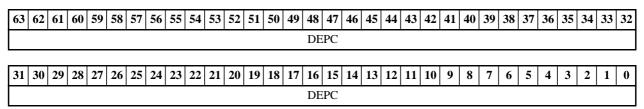

| Figure 6-22: DEPC Register                                             |     |

| Figure 6-23: Performance Counter Control Register                      |     |

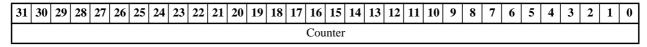

| Figure 6-24: Performance Counter Count Register                        |     |

| Figure 6-25: ErrCtl Register                                           |     |

| Figure 6-26: CacheErr Register                                         |     |

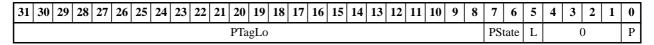

| Figure 6-27: TagLo Register                                            |     |

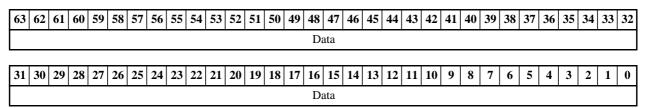

| Figure 6-28: DataLo Register                                           |     |

|                                                                        |     |

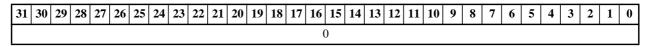

| Figure 6-29: TagHi Register                                            |     |

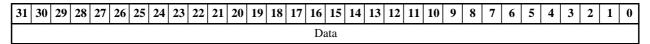

| Figure 6-30: DataHi Register                                           |     |

| Figure 6-31: ErrorEPC Register                                         |     |

| Figure 6-32: DESAVE Register                                           |     |

| Figure 8-1: 5K Cache Subsystem Organization                            |     |

| Figure 8-2: Cache RAM Formats                                          |     |

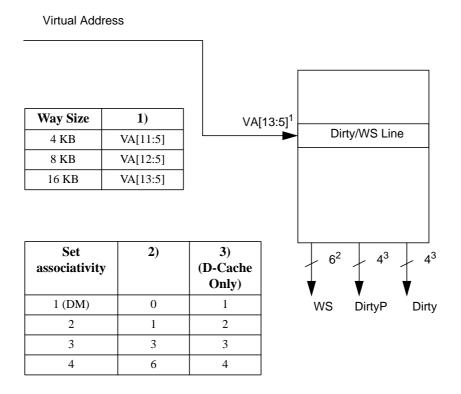

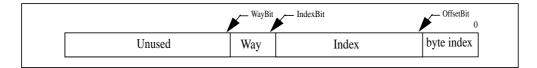

| Figure 8-3: Cache Data and Tag Indexing                                |     |

| Figure 8-4: Way Selection Indexing                                     |     |

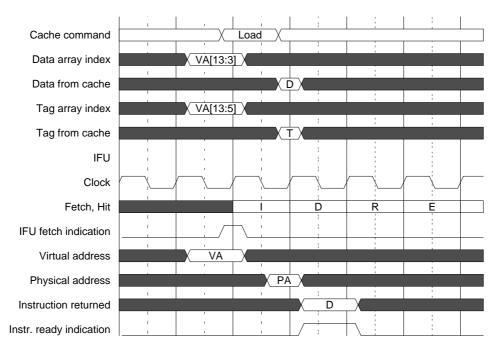

| Figure 8-5: Example of Instruction Fetch with ITLB Hit and Cache Hit   |     |

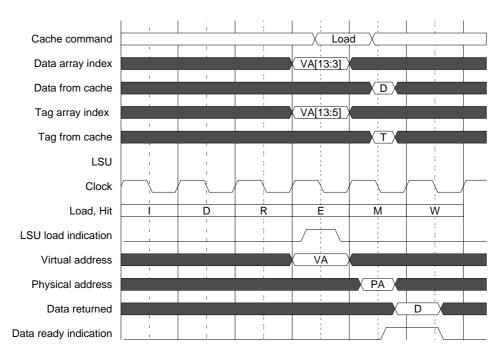

| Figure 8-6: Example of Data Load with DTLB Hit and Cache Hit           |     |

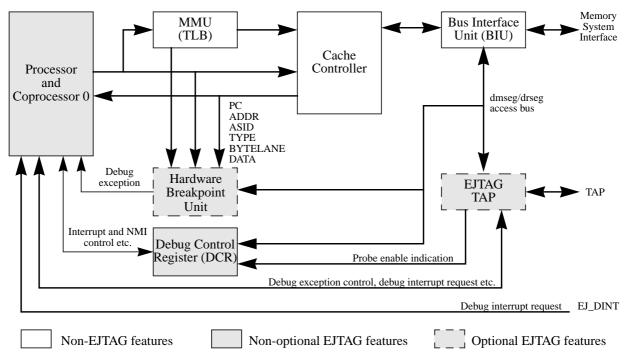

| Figure 10-1: Simplified Block Diagram of EJTAG Components              |     |

| Figure 10-2: DCR Register Format                                       |     |

| Figure 10-3: Instruction Breakpoint                                    |     |

| Figure 10-4: Data Breakpoint                                           |     |

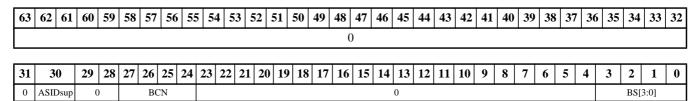

| Figure 10-5: IBS Register Format                                       |     |

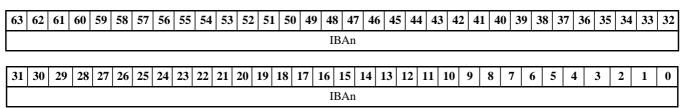

| Figure 10-6: IBAn Register Format                                      |     |

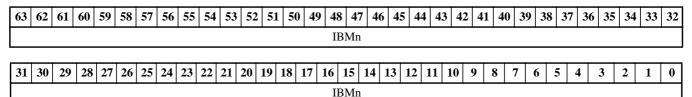

| Figure 10-7: IBMn Register Format.                                     |     |

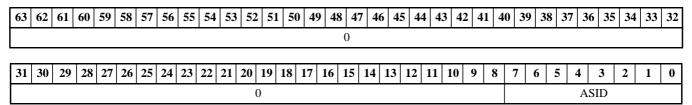

| Figure 10-8: IBASIDn Register Format                                   | 182 |

| Figure 10-9: IBCn Register Format                                      | 183 |

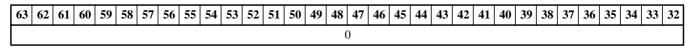

| Figure 10-10: DBS Register Format                                      | 184 |

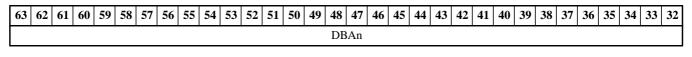

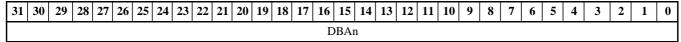

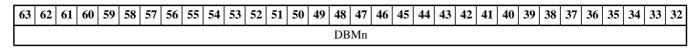

| Figure 10-11: DBAn Register Format                                     | 185 |

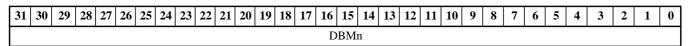

| Figure 10-12: DBMn Register Format                                     | 185 |

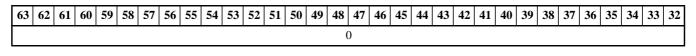

| Figure 10-13: DBASIDn Register Format                                  | 186 |

| Figure 10-14: DBCn Register Format                                     |     |

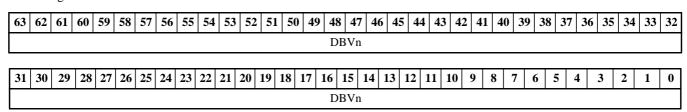

| Figure 10-15: DBVn Register Format                                     |     |

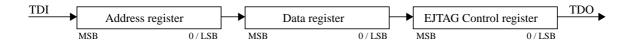

| Figure 10-16: Selected Registers when ALL Instruction is Selected      |     |

| Figure 10-17: Selected Registers when FASTDATA Instruction is Selected |     |

| Figure 10-18: Device ID Register Format                                |     |

| Figure 10-19: Implementation Register Format                           |     |

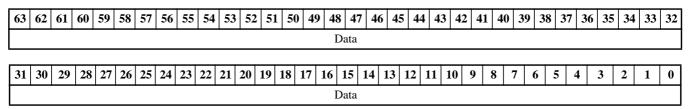

| Figure 10-20: Data Register Format                                     |     |

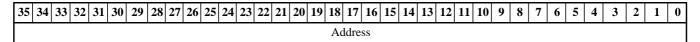

| Figure 10-21: Address Register Format                                  |     |

| Figure 10-22: EJTAG Control Register Format                            |     |

| Figure 10-23: Fastdata Register Format                                 |     |

| Figure 10-24: Bypass Register Format                                   |     |

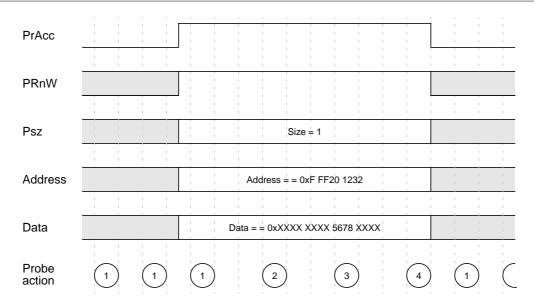

| Figure 10-25: Write Processor Access Example                           |     |

| Tigure 10-23. With Tiocessor Access Example                            | 203 |

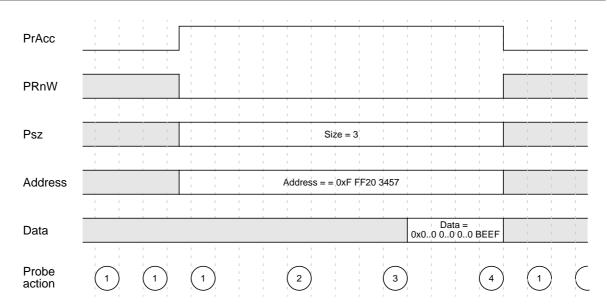

| Figure 10-26: Read Processor Access Example                  | 204 |

|--------------------------------------------------------------|-----|

| Figure 11-1: CPU Instruction Formats                         |     |

| Figure 12-1: Example Instruction Description                 |     |

| Figure 12-2: Example of Instruction Fields                   |     |

| Figure 12-3: Sample Bit Encoding Table                       |     |

| Figure 12-4: Usage of Address Fields to Select Index and Way |     |

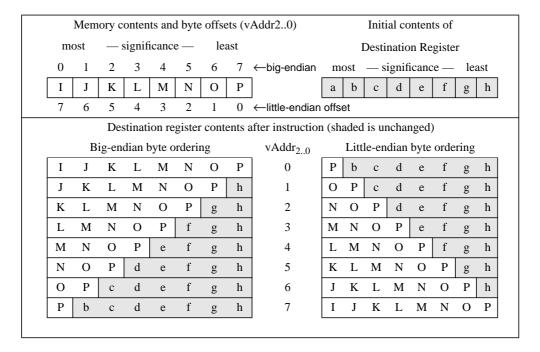

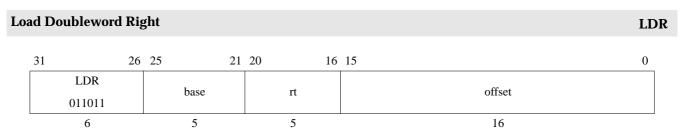

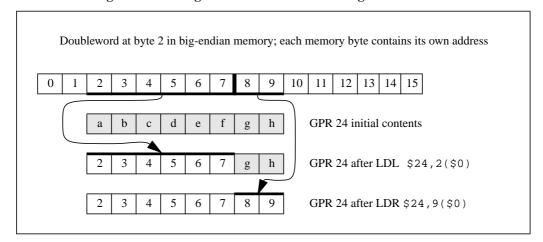

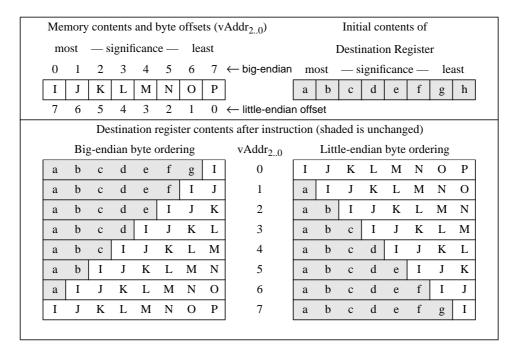

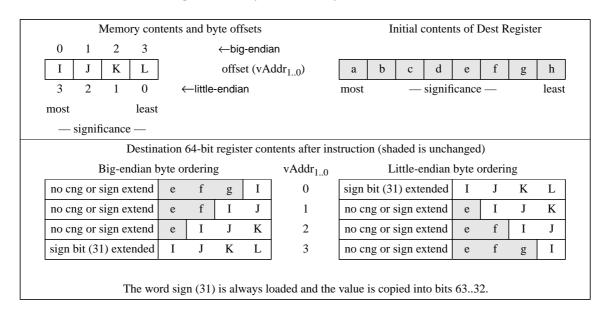

| Figure 12-5: Unaligned Doubleword Load Using LDL and LDR     |     |

| Figure 12-6: Bytes Loaded by LDL Instruction                 |     |

| Figure 12-7: Unaligned Doubleword Load Using LDR and LDL     |     |

| Figure 12-8: Bytes Loaded by LDR Instruction                 |     |

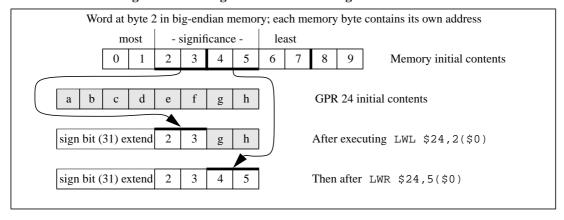

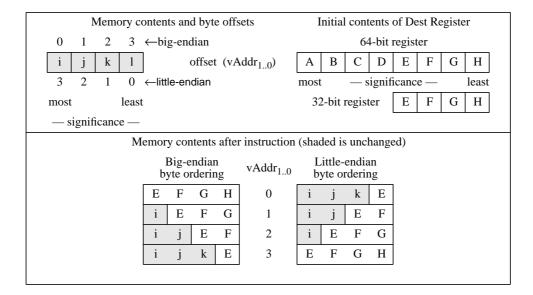

| Figure 12-9: Unaligned Word Load Using LWL and LWR           |     |

| Figure 12-10: Bytes Loaded by LWL Instruction                |     |

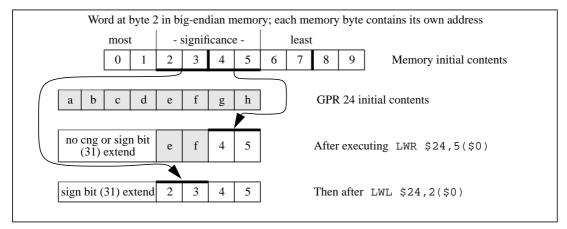

| Figure 12-11: Unaligned Word Load Using LWL and LWR          |     |

| Figure 12-12: Bytes Loaded by LWL Instruction                |     |

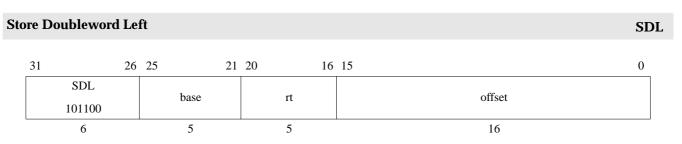

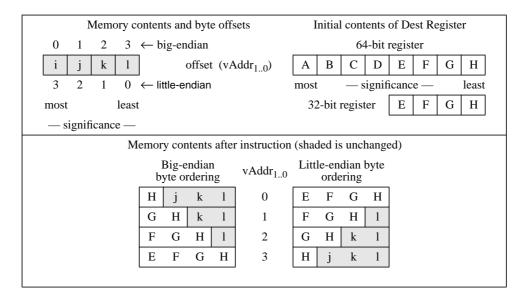

| Figure 12-13: Unaligned Doubleword Store With SDL and SDR    |     |

| Figure 12-14: Bytes Stored by an SDL Instruction             | 450 |

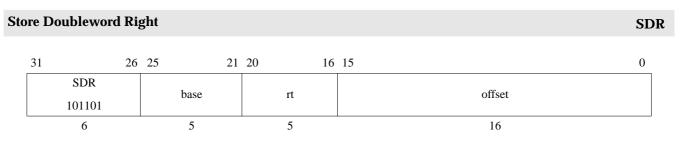

| Figure 12-15: Unaligned Doubleword Store With SDR and SDL    | 452 |

| Figure 12-16: Bytes Stored by an SDR Instruction             |     |

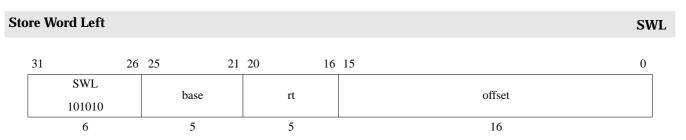

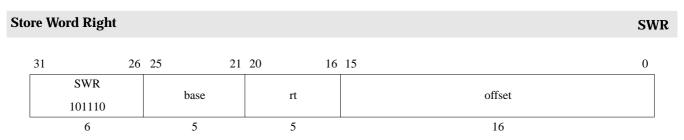

| Figure 12-17: Unaligned Word Store Using SWL and SWR         |     |

| Figure 12-18: Bytes Stored by an SWL Instruction             |     |

| Figure 12-19: Unaligned Word Store Using SWR and SWL         | 478 |

| Figure 12-20: Bytes Stored by SWR Instruction                | 479 |

|                                                              |     |

| MIPS64 <sup>™</sup> 5K <sup>™</sup> Processor Cor | e Family Software Use | r's Manual, Revision 02.08 |

|---------------------------------------------------|-----------------------|----------------------------|

|---------------------------------------------------|-----------------------|----------------------------|

# List of Tables

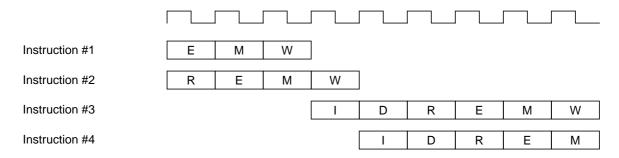

| Table 2-1: Arithmetic Coprocessor Instructions which can be Dual Issued                      | 13 |

|----------------------------------------------------------------------------------------------|----|

| Table 2-2: Non-Arithmetic Instructions which can be Dual Issued                              | 14 |

| Table 2-3: 5K Core Instruction Latencies                                                     |    |

| Table 2-4: 5K Core Instruction Repeat Rates                                                  |    |

| Table 2-5: Pipeline Interlocks                                                               | 22 |

| Table 2-6: Instruction Interlocks                                                            | 23 |

| Table 3-1: Parameters of Floating-Point Data Types                                           | 29 |

| Table 3-2: Value of Single or Double Floating-Point Data Type Encoding                       | 30 |

| Table 3-3: Value Supplied When a New Quiet NaN is Created                                    |    |

| Table 3-4: Coprocessor 1 Register Summary                                                    | 36 |

| Table 3-5: Read/Write Properties                                                             | 36 |

| Table 3-6: FIR Bit Field Descriptions                                                        | 37 |

| Table 3-7: FCCR Bit Field Descriptions                                                       | 38 |

| Table 3-8: FEXR Bit Field Descriptions                                                       |    |

| Table 3-9: FENR Bit Field Descriptions                                                       | 39 |

| Table 3-10: FCSR Bit Field Descriptions                                                      | 40 |

| Table 3-11: Cause, Enables, and Flags Definitions                                            |    |

| Table 3-12: Rounding Mode Definitions                                                        |    |

| Table 3-13: Zero Flushing for Tiny Results                                                   |    |

| Table 3-14: Handling of Denormalized Operand Values and Tiny Results Based on FS Bit Setting |    |

| Table 3-15: Handling of Tiny Intermediate Result Based on the FO and FS Bit Settings         |    |

| Table 3-16: Handling of Tiny Final Result Based on FN and FS Bit Settings                    |    |

| Table 3-17: Recommended FS/FO/FN Settings                                                    | 44 |

| Table 3-18: FPU Data Transfer Instructions                                                   |    |

| Table 3-19: FPU Loads and Stores Using Register+Offset Address Mode                          | 46 |

| Table 3-20: FPU Loads and Stores Using Register+Register Address Mode                        |    |

| Table 3-21: FPU Move To and From Instructions                                                |    |

| Table 3-22: FPU IEEE Arithmetic Operations                                                   | 47 |

| Table 3-23: FPU-Approximate Arithmetic Operations                                            |    |

| Table 3-24: FPU Multiply-Accumulate Arithmetic Operations                                    | 48 |

| Table 3-25: Supported Operand Range for Convert Instructions                                 | 48 |

| Table 3-26: FPU Conversion Operations Using the FCSR Rounding Mode                           | 49 |

| Table 3-27: FPU Conversion Operations Using a Directed Rounding Mode                         | 49 |

| Table 3-28: FPU Formatted Operand Move Instruction                                           | 50 |

| Table 3-29: FPU Conditional Move on True/False Instructions                                  | 50 |

| Table 3-30: FPU Conditional Move on Zero/Non-Zero Instructions                               | 50 |

| Table 3-31: FPU Conditional Branch Instructions                                              | 50 |

| Table 3-32: Deprecated FPU Conditional Branch Likely Instructions                            | 51 |

| Table 3-33: CPU Conditional Move on FPU True/False Instructions                              | 51 |

| Table 3-34: Result for Exceptions Not Trapped                                                | 52 |

| Table 3-35: 5Kf Core FPU Latency and Repeat Rate                                             | 56 |

| Table 4-1: Physical Address Generation                                                       | 63 |

| Table 4-2: TLB Exceptions                                                                    | 65 |

| Table 4-3: Virtual Address Spaces                                                            | 69 |

| Table 4-4: Address Space Access and TLB Refill Selection as a Function of Operating Mode     | 70 |

| Table 4-5: Address Translation and Cache Attributes for kseg0 and kseg1                      | 72 |

| Table 4-6: Address Translation and Cache Attributes for xkphys                               | 73 |

| Table 4-7: Physical Address and Cache Attribute for dseg                                     |    |

| Table 4-8: CPU Access to dseg Address Range                                                  |    |

| Table 5-1: Priority of Exceptions                                                            |    |

| Table 5-2: Exception Vector Base Addresses                                   | 81  |

|------------------------------------------------------------------------------|-----|

| Table 5-3: Exception Vector Offsets                                          |     |

| Table 5-4: Exception Vectors                                                 |     |

| Table 5-5: Mapping of Interrupts to the Cause and Status Registers           |     |

| Table 5-6: Exceptions In Debug Mode                                          |     |

| Table 6-1: Coprocessor 0 Register Summary                                    |     |

| Table 6-2: Read/Write Properties                                             |     |

| Table 6-3: Index Register Field Descriptions.                                |     |

| Table 6-4: Random Register Field Descriptions                                |     |

| Table 6-5: 32-bit EntryLo0, EntryLo1 Register Field Descriptions             |     |

| Table 6-6: Cache Coherency Attributes                                        |     |

| Table 6-7: Context Register Field Descriptions                               |     |

| Table 6-8: PageMask Register Field Descriptions                              |     |

| Table 6-9: Values for the Mask Field of the PageMask Register                |     |

| Table 6-10: Wired Register Field Descriptions                                |     |

| Table 6-11: BadVAddr Register Field Descriptions                             |     |

| Table 6-12: Count Register Field Descriptions                                |     |

|                                                                              |     |

| Table 6-13: 64-bit EntryHi Register Field Descriptions                       |     |

| Table 6-14: Compare Register Field Descriptions  Table 6-15: Processor Modes |     |

|                                                                              |     |

| Table 6-16: Status Register Field Descriptions                               |     |

| Table 6-17: Cause Register Field Descriptions                                |     |

| Table 6-18: Cause Register ExcCode Field                                     |     |

| Table 6-19: EPC Register Field Descriptions                                  |     |

| Table 6-20: PRId Register Field Descriptions.                                |     |

| Table 6-21: Config Register Field Descriptions.                              |     |

| Table 6-22: Config1 Register Field Descriptions                              |     |

| Table 6-23: WatchLo Register Field Descriptions                              | 124 |

| Table 6-24: WatchHi Register Field Descriptions                              |     |

| Table 6-25: XContext Register Fields                                         |     |

| Table 6-26: Debug Register Field Descriptions                                |     |

| Table 6-27: DEPC Register Field Descriptions                                 |     |

| Table 6-28: Performance Counter Register Selects                             |     |

| Table 6-29: Performance Counter Control Register Field Descriptions          |     |

| Table 6-30: Performance Counter Count Register Field Descriptions            |     |

| Table 6-31: Performance Counter Count Register Field Descriptions            |     |

| Table 6-32: ErrCtl Register Field Descriptions                               |     |

| Table 6-33: CacheErr Register Field Descriptions                             |     |

| Table 6-34: TagLo Register Field Descriptions                                |     |

| Table 6-35: DataLo Register Field Descriptions                               |     |

| Table 6-36: TagHi Register Field Descriptions                                |     |

| Table 6-37: DataHi Register Field Descriptions                               | 139 |

| Table 6-38: ErrorEPC Register Field Descriptions                             | 139 |

| Table 6-39: DESAVE Register Fields                                           | 140 |

| Table 8-1: Way Selection Encoding, 4 Ways                                    | 152 |

| Table 8-2: Way Selection Encoding, 3 Ways                                    | 152 |

| Table 8-3: Way Selection Encoding, 2 Ways                                    | 152 |

| Table 8-4: Action on PREF and PREFX Instructions                             | 153 |

| Table 8-5: Invalid WS Fields Not Causing Errors                              | 154 |

| Table 8-6: Association of Ways and Bits in the WS Field                      |     |

| Table 10-1: Register Field Read/Write Notations                              |     |

| Table 10-2: SYNC Instruction References                                      |     |

| Table 10-3: "Required" CP0 and dseg Hazard Spacing                           |     |

| Table 10-4: Coprocessor 0 Registers for EJTAG                                |     |

| Table 10-5: Physical Address and Cache Attribute for dseg, dmseg and drseg   |     |

|                                                                                     | 1.67 |

|-------------------------------------------------------------------------------------|------|

| Table 10-6: Access to dmseg Address Range                                           |      |

| Table 10-7: Access to drseg Address Range                                           |      |

| Table 10-8: DCR Register Field Descriptions                                         |      |

| Table 10-9: Instruction Breakpoint Register Summary                                 |      |

| Table 10-10: Data Breakpoint Register Summary                                       |      |

| Table 10-11: Instruction Breakpoint Condition Parameters                            |      |

| Table 10-12: Data Breakpoint Condition Parameters                                   |      |

| Table 10-13: BYTELANE Value at Unaligned Address                                    |      |

| Table 10-14: Behavior on Precise Exceptions from Data Breakpoints                   |      |

| Table 10-15: Rules for Updating BS Bits on Precise Exceptions from Data Breakpoints |      |

| Table 10-16: Rules for Updating BS Bits on Data Triggerpoints                       |      |

| Table 10-17: Instruction Breakpoint Register Mapping                                |      |

| Table 10-18: IBS Register Field Descriptions                                        |      |

| Table 10-19: IBAn Register Field Descriptions                                       |      |

| Table 10-20: IBMn Register Field Descriptions                                       |      |

| Table 10-21: IBASIDn Register Field Descriptions                                    |      |

| Table 10-22: IBCn Register Field Descriptions                                       |      |

| Table 10-23: Data Breakpoint Register Mapping                                       |      |

| Table 10-24: DBS Register Field Descriptions                                        |      |

| Table 10-25: DBAn Register Field Descriptions                                       |      |

| Table 10-26: DBMn Register Field Descriptions                                       |      |

| Table 10-27: DBASIDn Register Field Descriptions                                    |      |

| Table 10-28: DBCn Register Field Descriptions                                       |      |

| Table 10-29: DBVn Register Field Descriptions                                       |      |

| Table 10-30: TAP Instruction Overview                                               |      |

| Table 10-31: EJTAG TAP Data Registers                                               |      |

| Table 10-32: Device ID Register Field Descriptions                                  |      |

| Table 10-33: Implementation Register Field Descriptions                             |      |

| Table 10-34: Data Register Field Descriptions                                       |      |

| Table 10-35: Data Register Contents                                                 |      |

| Table 10-36: Address Register Field Descriptions.                                   |      |

| Table 10-37: EJTAG Control Register Field Descriptions                              |      |

| Table 10-38: Combinations of ProbTrap and ProbEn                                    |      |

| Table 10-39: Fastdata Register Field Description                                    |      |

| Table 10-40: Operation of the FASTDATA access                                       | 201  |

| Table 10-41: Bypass Register Field Description                                      | 202  |

| Table 10-42: Information Provided to Probe at Processor Access                      | 202  |

| Table 11-1: Byte Access Within a Doubleword                                         | 208  |

| Table 12-1: 5K CP0 Hazard Description Table                                         |      |

| Table 12-2: 5K CP0 Hazards and Calculated Delay Times                               | 219  |

| Table 12-3: 5K Core Family Common Instruction Set                                   | 220  |

| Table 12-4: 5Kf Floating Point Instruction Set                                      |      |

| Table 12-5: Symbols Used in the Instruction Encoding Tables                         |      |

| Table 12-6: Encoding of the Opcode Field                                            | 230  |

| Table 12-7: SPECIAL Opcode Encoding of Function Field                               | 230  |

| Table 12-8: REGIMM Encoding of rt Field                                             |      |

| Table 12-9: SPECIAL2 Encoding of Function Field                                     |      |

| Table 12-10: MOVCI Encoding of tf Bit                                               |      |

| Table 12-11: COP0 Encoding of rs Field                                              |      |

| Table 12-12: COP0 Encoding of Function Field When rs=CO                             |      |

| Table 12-13: COP1 Encoding of rs Field                                              |      |

| Table 12-14: COP1 Encoding of rt Field When rs=BC1                                  | 232  |

| Table 12-15: COP1 Encoding of Function Field When rs=S                              |      |

| Table 12-16: COP1 Encoding of Function Field When rs=D                              |      |

| Table 12-17: COP1 Encoding of Function Field When rs=W or L                         |      |

| Table 12-18: COP1 Encoding of tf Bit When rs=S or D, Function=MOVCF                 | 233 |

|-------------------------------------------------------------------------------------|-----|

| Table 12-19: COP1X Encoding of Function Field                                       |     |

| Table 12-20: COP2 Encoding of rs Field                                              |     |

| Table 12-21: COP2 Encoding of rt Field When rs=BC2                                  | 233 |

| Table 12-22: FPU Comparisons Without Special Operand Exceptions                     |     |

| Table 12-23: FPU Comparisons With Special Operand Exceptions for QNaNs              |     |

| Table 12-24: Usage of Effective Address                                             | 286 |

| Table 12-25: Encoding of Bits[17:16] of CACHE Instruction                           | 287 |

| Table 12-26: Encoding of Bits [20:18] of the CACHE Instruction, ErrCtl[WST] Cleared | 288 |

| Table 12-27: Encoding of Bits [20:18] of the CACHE Instruction, ErrCtl[WST] Set     | 290 |

| Table 12-28: Values of the <i>hint</i> Field for the PREF Instruction               | 426 |

# Introduction

This chapter provides an introduction to the MIPS Technologies MIPS64<sup>TM</sup> 5K<sup>TM</sup> microprocessor core family, with as description of the different members, the 5Kc and 5Kf cores. It contains the following sections:

- Section 1.1, "Overview"

- Section 1.2, "Features"

- Section 1.3, "Core Block Diagram"

#### 1.1 Overview

The MIPS64 5K is a synthesizable, highly-integrated 64-bit MIPS® RISC microprocessor core designed for high-performance, low-power, low-cost embedded applications. The 5K core is portable across processes, is highly configurable, and is integrated easily into standard design flows. It incorporates powerful instructions for embedded applications, as well as proven memory-management and privileged mode control mechanisms.

The 5K core executes the MIPS64<sup>TM</sup> instruction set architecture (ISA), which is a superset of the MIPS V<sup>TM</sup> architecture, and includes special multiply-accumulate, conditional move, prefetch, wait, and leading zero/one detect instructions. To allow easy migration from 32-bit processors, the 5K provides a 32-bit compatibility mode, in which code compiled for MIPS32<sup>TM</sup> processors can run unaltered.

The 5Kf also core also features a high performances IEEE 754 compliant Floating Point Unit (FPU). The FPU supports both single and double precision instructions. It includes the multiply add instruction, which can issue every cycle, whereby both a multiply and an add single precision operation can be performed in every cycle. The 5Kf core can dual issue a floating point arithmetic instruction with a floating point load/store or integer instruction, whereby two instructions can be executed every cycle in floating point applications. A coprocessor interface is also provided, which allows designers a way to easily extend their architectures by addition of custom functionality, such as network, or graphics coprocessors.

The multiply-divide unit (MDU) supports a maximum issue rate of one 32x16 multiply (MUL), multiply-add (MADD/MADDU), or multiply-subtract (MSUB/MSUBU) operation per clock, or one 32x32 MUL, MADD, or MSUB every other clock, or one 64x64 DMULT/DMULTU every 9 clocks.

The memory management unit contains a configurable 16, 32, or 48 dual-entry Joint TLB (JTLB) with variable page sizes, a 4-entry Instruction micro TLB (ITLB), and a 4-entry Data micro TLB (DTLB). Using a TLB with the 5K core is optional. The alternative is to use a far simpler Fixed Mapping Translation (FMT) scheme.

Optional instruction and data caches are fully programmable from 0 - 64 Kbytes in size, with a maximum size of 16 Kbytes/way in a 4-way, set-associative implementation. In addition, each cache can be organized as direct-mapped, 2-way, 3-way, or 4-way set-associative. The 5K supports an instruction- scheduling mechanism that reduces pipeline stalls on cache misses and also supports hit-under-miss processing in the data cache. Both caches are virtually indexed and physically tagged. Virtual indexing allows the cache to be indexed in the same clock cycle in which the address is translated.

To ease software debugging, the EJTAG debug solution in the 5K core includes instruction software breakpoints, a single-step feature, and a dedicated Debug Mode. Optional hardware breakpoints include 4 instruction and 2 data breakpoints. An optional Test Access Port (TAP) forms the interface to an external debug host and provides a dedicated communication channel for debugging of an embedded system.

#### 1.2 Features

- 64-bit Data and Address Path (42-bit virtual and 36-bit physical address space)

- MIPS64 Compatible Instruction Set

- Based on MIPS VTM instruction set architecture

- Multiply-accumulate and multiply-subtract instructions (MADD, MADDU, MSUB, MSUBU)

- Targeted multiply instruction (MUL)

- Zero/One detect instructions (CLZ, CLO, DLCO, DCLZ)

- Wait instruction (WAIT)

- Conditional move instructions (MOVZ, MOVN)

- Prefetch instructions (PREF, PREFX)

- Dual-issue Floating Point Unit / Coprocessor 1 (5Kf core only)

- Fully pipelined IEEE 754 compliant floating point unit with both single and double precision instructions

- Includes multiply add instruction

- Maximum issue rate of one multiply add single (MADD.S) instruction every clock

- Maximum issue rate of one multiply add double (MADD.D) instruction every other clock

- FPU executes independently of integer pipeline

- Fast flush-to-zero mode to optimize performance

- Dual-issue superscalar micro-architecture capable of executing (5Kf core only):

- 1 integer and 1 arithmetic floating point instruction

- 1 floating point arithmetic and 1 floating point load/store instruction

- General Purpose Coprocessor Interface

- Supports both COP1 and COP2 coprocessors for 5Kc, and COP2 coprocessor for 5Kf

- Supports all MIPS V instructions, including advanced COP1X instructions for 5Kc

- Utilizes high-performance features of the integer unit

- Dual-issue capable interface supports execution of an arithmetic coprocessor instruction, and an integer or coprocessor load/store instruction every cycle

- Utilizes high-performance features of the integer unit

- Programmable Cache Sizes

- Individually configurable instruction and data caches

- Sizes from 0 16 KBytes/way (64 KBytes maximum)

- Direct-mapped, 2-, 3-, or 4-Way Set Associative

- Non-blocking loads and prefetches

- 32-byte cache line size, doubleword sectored

- Virtually indexed, physically tagged

- Cache line locking support

- Optional parity protection

- MIPS64 privileged resource architecture

- Count/Compare registers for real-time timer interrupts

- Instruction and Data watch registers for software breakpoints

- Separate interrupt exception vector

- Supervisor Mode operation

- Performance Monitoring logic for analyzing application speed

- Programmable Memory Management Unit

- 16, 32, or 48 dual-entry JTLB with variable page sizes

- 4-entry instruction micro TLB

- 4-entry data micro TLB

- Support for 8-bit ASID

- Support for 4KB 16MB page sizes

- Simple Bus Interface Unit (BIU)

- All I/Os fully registered

- Separate unidirectional 36-bit address and 64-bit data buses

- 32-byte write buffer (4 doublewords)

- 1-line (32-byte) eviction buffer

- Multiply/Divide Unit

- Max issue rate of one 32x16 multiply per clock

- Max issue rate of one 32x32 multiply every other clock

- Max issue rate of one 64x64 multiply every nine clocks

- 37 clock latency on 32/32 divides.

- 69 clock latency on 64/64 divides

- Early-in feature for divides allows results sooner for smaller dividend values

- Power Control

- Minimum frequency is 0 MHz

- Power-down mode (triggered by WAIT instruction)

- Support for software-controlled clock divider

- Sleep Mode: During this mode, the clocks are shut off. Sleep mode is entered automatically from power-down mode after all bus activity stops.

- EJTAG Debug Support

- Software Debug Breakpoint instruction (SDBBP)

- Single-step feature

- Debug Mode

- Optional hardware breakpoints (4 instruction and 2 data breakpoints)

- Optional Test Access Port (TAP) interface to debug host

#### 1.3 Core Block Diagram

The basic blocks that comprise the 5K core are shown for the 5Kc core in Figure 1-1 and for the 5Kf core in Figure 1-2. Blocks that are optional are shown as shaded. The optional blocks can be added to the 5K core, depending on the particular requirements of an implementation.

Figure 1-1 5Kc Core Block Diagram

Figure 1-2 5Kf Core Block Diagram

Each block is described individually in the remaining sections of this chapter.

#### 1.3.1 Execution Unit

The 5K core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract). The 5K core contains thirty-two, 64-bit general-purpose registers used for scalar integer operations and address calculation. The register file consists of two read ports and two write ports and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

• 64-bit adder used for calculating arithmetic results and data addresses

- · Address unit for calculating the next instruction address

- · Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instructions streams in which data-producing instructions are followed closely by consumers of their results

- Zero/One detect unit for implementing the CLZ, DCLZ and CLO, DCLO instructions

- Logic Unit for performing bitwise logical operations

- Shifter & Store Aligner

#### 1.3.2 Floating Point Unit (FPU) / Coprocessor 1 (5Kf core only)

The 5Kf core Floating Point Unit (FPU) implements the MIPS64 ISA (Instruction Set Architecture) for floating-point computation. The implementation supports the ANSI/IEEE Standard 754 (IEEE Standard for Binary Floating-Point Arithmetic). The hardware supports IEEE single and double precision data formats. The performance is optimized for single precision formats. Most instructions have a 1 cycle throughput and 4 cycle latency. The FPU contains thirty-two 64-bit floating-point registers used for floating point operations.

The FPU implements the MIPS64 multiply-add (MADD) and multiply-sub (MSUB) instructions with intermediate rounding after the multiply function. The result is guaranteed to be the same as executing a MUL and an ADD instruction separately, but the instruction latency, instruction fetch, dispatch bandwidth, and the total number of register accesses are improved. A fast Flush-to-Zero mode is implemented to optimize performance. IEEE denormalized input operands are supported by hardware for some instructions. IEEE denormalized result operands are not supported by hardware.

The FPU has a separate pipeline for floating point instruction execution. This pipeline operates in parallel with the integer unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows long-running FPU operations, such as divides or square root, to be partially masked by system stalls and/or other integer unit instructions. Instructions are always dispatched and completed in order. The exception model is 'precise' at all times. The FPU is also denoted coprocessor 1.

For additional information, refer to Chapter 3, "Floating-Point Unit."

#### 1.3.3 Multiply/Divide Unit (MDU)

The Multiply/Divide unit performs multiply and divide operations. The MDU supports execution of a 16x16 or 32x16 multiply operation every clock cycle. 32x32 multiply operations can be issued every other clock cycle, and 64x64 multiply operations can be issued every nine clock cycles. Appropriate interlocks are implemented to stall the issue of back-to-back 32x32 and 64x64 multiply operations. Multiply operand size is automatically determined by logic in the MDU.

The MDU contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the integer unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows long, multicycle MDU operations (such as a divide) to be partially masked from system stalls and other integer unit instructions. To achieve the highest possible performance, the MDU contains a 32x16 Booth-recoded multiply array, and each class of multiply instructions is processed in a different way, so as to best utilize available resources.

Divide operations are implemented with a simple 1 bit-per-clock iterative algorithm. A 32-bit divide requires 37 clock cycles to complete, while a 64-bit divide requires 69 clock cycles. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed. However, the divider has an early-in feature which detects the size of the dividend in 8-bit increments, so that when a smaller dividend is detected, the algorithm reduces the number of iterations accordingly.

For additional information, refer to Chapter 2, "Pipeline."

#### 1.3.4 System Control Coprocessor (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation and cache protocols, the exception control system (for example, interrupts enabled or disabled), the operating modes (Kernel, Supervisor, User, or Debug Mode), and the processor's diagnostics capability. Configuration information such as cache size and set associativity is available by accessing the CP0 registers.

For additional information, refer to Chapter 6, "Coprocessor 0 Registers."

#### 1.3.5 Memory Management Unit (MMU)

The 5K core contains an MMU that interfaces between the execution unit and the cache controller. The MMU supports two types of address translation mechanisms, either of which can be implemented:

- Translation lookaside buffer (TLB)

- Fixed Mapping Translation (FMT)

The TLB consists of three address translation buffers, a 16, 32, or 48 dual-entry fully associative Joint TLB (JTLB), a 4-entry fully associative Instruction TLB (ITLB), and a 4-entry fully associative Data TLB (DTLB).

For additional information, refer to Chapter 4, "Memory Management."

#### 1.3.6 Cache Controllers & Bus Interface

The instruction and data cache controllers support caches of various sizes, organizations, and set-associativity. For example, the data cache can be 8 Kbytes in size and 2-way set-associative, while the instruction cache can be 16 Kbytes in size and 4-way set-associative. In addition, each cache has its own 64-bit data path, and both caches can be accessed in the same pipeline clock cycle.

The Bus Interface Unit (BIU) controls the external interface signals.

For additional information, refer to Chapter 8, "Cache Organization and Operation."

#### 1.3.7 Power Management

The 5K microprocessor core offers a number of power-management features, including low-power design, active power management, and power-down modes of operation. The core is a static design that supports a WAIT instruction, designed to signal the rest of the system that execution and clocking should be halted, thereby reducing system power consumption during idle periods.

For additional information, refer to Chapter 9, "Power Management."

#### 1.3.8 Instruction and Data Caches

The 5K core supports optional, on-chip instruction and data caches that can each be accessed in a single processor cycle. The caches are virtually indexed and physically tagged, allowing the virtual-to-physical address translation to occur in parallel with the cache access, rather than having to wait for the physical address translation.

While cache refills are in progress, the caches can continue processing hits. Streaming is also supported, in which instructions and data are forwarded during cache refills. Cache performance is further enhanced by special logic that implements a least-recently used (LRU) algorithm for way selection when a cache line is replaced.

The 5K core supports instruction cache locking. This feature allows critical code and data segments to be locked into the cache, enabling the system designer to maximize the efficiency of the system cache. For the data cache, the locked contents can be updated on a store hit, but cannot be selected for replacement on a store miss. Cache locking is always enabled on all cache entries—entries can be marked as locked or unlocked on a per-line basis using the CACHE instruction.

For additional information, refer to Chapter 8, "Cache Organization and Operation."

#### 1.3.9 EJTAG Debug Support

The 5K core provides an optional Enhanced JTAG (EJTAG) interface for use in software debugging of application and operating-system code. In addition to standard User, Supervisor, and Kernel Modes, the 5K core provides a Debug Mode which is entered after a Debug exception is taken and continues until a Debug Exception Return (DERET) instruction is executed.

For additional information, refer to Chapter 5, "Exception Processing," and Chapter 10, "EJTAG Debug Features."

# Pipeline

Chapter 2 describes the 5K processor core instruction pipeline. The pipeline includes a six-stage integer pipeline and a separate execution pipeline for multiply and divide operations. The two pipelines operate in parallel.

This chapter contains the following sections:

- Section 2.1, "Pipeline Stages"

- Section 2.2, "Instruction Fetch"

- Section 2.3, "Branch Delay"

- Section 2.4, "Limited Dual Issue"

- Section 2.5, "Instruction Fetching from Uncached Memory Space"

- Section 2.6, "Data Access"

- Section 2.7, "Instruction Scheduling"

- Section 2.8, "MDU Pipeline"

- Section 2.9, "Slip Conditions and Interlock Handling"

## 2.1 Pipeline Stages

The integer pipeline consists of the following six stages:

- Instruction Fetch (I Stage)

- Instruction Dispatch (D Stage)

- Register File Read (R Stage)

- Instruction Execution (E Stage)

- Memory Access (M Stage)

- Writeback (W stage)

The 5K core implements a bypass mechanism that allows the result of an operation to be forwarded directly to the instruction that needs it, without having to write the result to the register and then read it back.

Figure 2-1 shows the operations performed in each pipeline stage.

Figure 2-1 Pipeline Stages

#### 2.1.1 I Stage: Instruction Fetch

During the I stage:

- Instruction(s) are fetched from the instruction cache.

- The instruction translation lookaside buffer (ITLB) performs the virtual-to-physical address translation.

#### 2.1.2 D Stage: Instruction Dispatch

During the D stage:

- Branch decode and prediction.

- Instruction dispatch to coprocessor/integer unit.

## 2.1.3 R Stage: Register File Read

During the R stage:

- The GPR register file is read.

- The instruction is decoded.

#### 2.1.4 E Stage: Execution

During the E stage:

- The Arithmetic Logic Unit (ALU) performs the arithmetic or logical operation for register-to-register instructions.

- The ALU determines whether the branch condition is true.

- All multiply and divide operations begin in this stage.

- The ALU calculates the full virtual address for load and store instructions.

- The cache look-up starts for loads and stores.

#### 2.1.5 M Stage: Memory Access

During the M stage:

- The data translation lookaside buffer (DTLB) performs the virtual-to-physical address translation.

- Data cache look-up completes.

- · Loaded data is aligned.

#### 2.1.6 W Stage: Writeback

During the W stage:

• For register-to-register or load instructions, the result is written back to the register file.

#### 2.2 Instruction Fetch

The 5K processor maintains a three-entry doubleword instruction buffer, which can store up to six instructions. The instruction buffer includes the following features:

- Speculative fetching of several instructions.

- Intelligent handling of instruction cache misses.

- Minimization of penalty for branches and jumps.

Using speculative instruction fetching, the instruction buffer can keep ahead of the rest of the pipeline by prefetching instructions which may be dispatched at a later time. Instruction-cache refills are potentially initiated early, thus minimizing delays in the pipeline.

To avoid unnecessary instruction-cache refills, the instruction buffer employs a conservative, intelligent cache-refill scheme, ensuring that a cache line is refilled only if it contains an instruction which is certain to be dispatched to the execution pipeline. For example, speculative refills are performed only if there are no jumps or branches in the instruction buffer.

When a branch instruction is recognized, the instruction buffer ensures that one entry contains the branch target and one entry contains the instruction after the branch delay slot. The instruction buffer predicts all branch instructions to be taken. Correctly predicted branches impose no pipeline delay. When the branch is mispredicted (not taken), the total penalty will be only one pipeline bubble (as explained in Section 2.3, "Branch Delay").

Note that the JR and JALR instructions always cause one pipeline bubble because of the interlock resulting from a data dependency on the source register.

When required by the instruction buffer, the instruction cache is accessed. The instruction address is translated to determine if the required instruction resides in the cache. If it does not, an instruction-cache miss occurs.

When a cache miss is detected, the fetch request is issued on the external bus. If the instruction buffer is empty, the I stage is slipped (refer to Section 2.9, "Slip Conditions and Interlock Handling"). When the instruction is returned, the I-stage slip is released, and the instruction is written to the instruction register for immediate use.

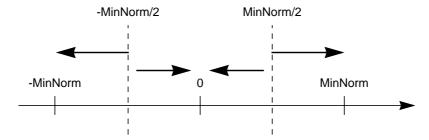

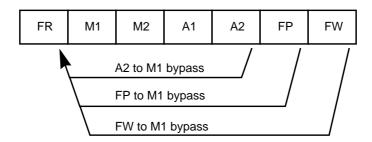

#### 2.3 Branch Delay